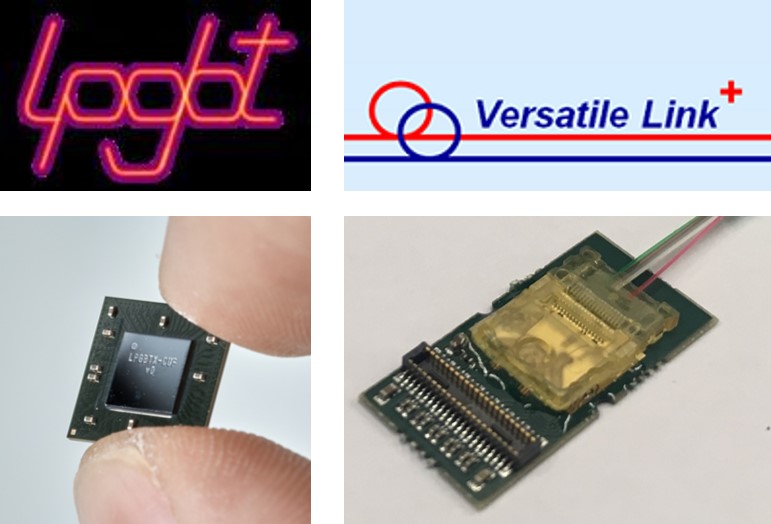

EP-ESE is designing the next generation of electronic and opto-electronic components to provide a low-power 10 Gbps radiation-tolerant link for bidirectional data transmission. Power consumption of the electronics is minimised and the components are compact and light to cope with the requirements of the HL-LHC detectors.

The main ASIC is a SERDES called the low-power GigaBit Transceiver (lpGBT). The opto-electronic system is known as the Versatile Link +. This comprises the custom-designed Versatile Transceiver-plus (VTRX+) for mounting on the detectors, passives components, and commercial transceivers for the back-end electronics, specially qualified for this application.

A demonstrator board comprising these components, the Versatile Link Demonstrator Board+ (VLDB+), is also available.

HDL code has been designed for implementation in FPGAs in the back-end electronics and is supported for different frameworks. This is called the lpGBT-FPGA.

User support is available here and by emailing lpgbt-support@cern.ch

Ordering procedure

These components are in production. Clients are strongly encouraged to announce their production quantities as soon as possible. If you are in one of the LHC experiments, please address your request to your electronics coordinator:

Alex Kluge for ALICE, Hucheng Chen for ATLAS, Magnus Hansen for CMS, Ken Wyllie for LHCb.

If you are not a member of an LHC experiment, please contact Ken Wyllie.