Radiation-hard high-speed data links play an ever-increasing role in modern HEP experiments. The state-of-the-art is the lpGBT and Versatile-Link+ ecosystem targetting the LHC Phase-II upgrades and providing data rates of 10 Gb/s. Beyond this, two lines of R&D activities have been identified to bring the performance of high-speed data links to the levels required by future detectors, namely custom opto-electronics and commercially-available FPGAs. The first of these is concentrating on the development of high-speed driver circuits for VCSELs and Silicon Photonics Modulators in synergy with research in IC technologies. The second line is to study modulation and coding schemes, and their implementation in FPGAs. More details are given below below. This R&D is pursued under the banner of the current CERN EP R&D programme on technologies for future experiments.

Silicon Photonics is a promising technology that could enable a new generation of highly-integrated, high-performance particle physics detectors. This technology uses standard ASIC production processes to pattern light-manipulating structures onto silicon wafers, which opens the door to custom designing optoelectronic devices and circuits, and would enable higher levels of integration between optics and electronics in future. We are investigating the radiation tolerance of devices, modelling the radiation response and working on device design to improve that tolerance and extend the reach of optical link technology into the innermost regions of future particle physics detectors. New optical systems architectures like Wavelength Division Multiplexing are also being investigated in order to understand all of the benefits this technology can offer.

Contact: Jan Troska

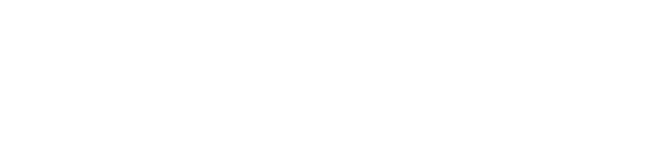

CERN silicon-photonics prototype chip (left) and ring-modulator structure (right).

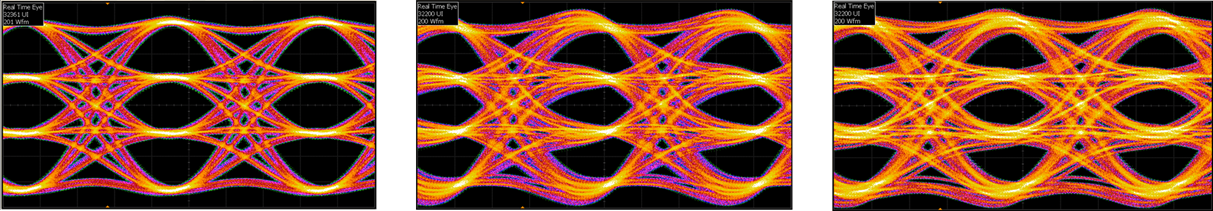

FPGAs are excellent back-end counterparts to the high-speed custom ASICs of the future detectors. The performance of high-end state-of-the-art FPGAs and commercial optical modules is already reaching line data rates of more than 50 Gbps and are characterized in this project. Specific standards like PAM-4 are investigated and encoding schemes are studied in order to identify potential candidates for future high-speed links, and provide practical tools and inputs to the ASIC design and testing activity.

Contact: Sophie Baron

Electrical PAM-4 eye diagrams generated by an FPGA.